Technologie de la famille CMOS

Introduction :

La logique numérique à MOS complémentaire, constituant des blocs de complexité SSI (intégration à très grande échelle) et MSI (intégration à moyenne échelle), a été accueillie comme la famille logique idéale. Elle a rapidement gagné en popularité et un nombre croissant de constructeurs l'utilise avec des prix de revient raisonnables.

Destinée à l'origine à des applications aérospatiales, la famille CMOS trouve actuellement sa vocation dans les instruments portables, dans l'électronique industrielle et médicale, l'automobile et les périphériques d'ordinateur et domine, en plus, le marché de l'horlogerie électronique.

Certains circuits CMOS, comme les commutateurs analogiques bidirectionnels, exploitent les propriétés uniques de la technologie CMOS ; d'autres tirent avantage du faible encombrement et des possibilités de haute densité permettant d'atteindre réellement la complexité LSI (intégration à grande échelle). Mais la plupart des circuits CMOS existant aujourd'hui sont de complexité SSI et MSI et exécutent des opérations logiques qui existent déjà depuis plusieurs années en technologie TTL. Par conséquent, il est à la fois utile et pratique de comparer le fonctionnement de la CMOS avec celui de la TTL, plus familière (figure 1). Beaucoup de boîtiers CMOS sont compatibles broche à broche avec leur homologue TTL, d'autres ne sont identiques que par leur fonctionnement et d'autres, enfin, ne sont que similaires et dans la plupart des cas offrent des avantages supplémentaires.

La vitesse de fonctionnement de la série CMOS est comparable à celle de la série 74L-TTL et DTL, et environ de trois à six fois plus faible que celle de la TTL ou de la Schottky faible puissance (LS-TTL). Le niveau d'immunité au bruit et la sortance sont quasiment

idéaux, la tension d'alimentation n'est pas critique et la consommation en courant au repos est inférieure de plusieurs puissances de dix à celle de n'importe quelle technologie concurrente.

Puissance dissipée

En fonctionnement statique, le transistor du canal P (tête) et le transistor du canal N (queue) ne conduisent pas en même temps et seul le courant de fuite circulant de +(VDD) à (VSS) de l'alimentation doit être pris en compte dans le calcul de la consommation. Ce courant de fuite est de 0,5 nA typique par porte, ce qui amène la puissance dissipée à une valeur très faible et très intéressante de 2,5 nW par porte (sous 5 volts).

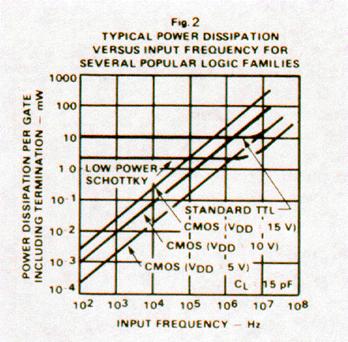

Chaque fois qu'un circuit CMOS fonctionne, lorsque les entrées de données ou d'horloge changent de niveau logique, il consomme un courant supplémentaire pour charger et décharger les capacités (des capacités parasites internes au boîtier et, également, la capacité de la charge). De plus, lors de chaque flanc, les deux transistors de sortie conduisent pendant un temps très bref. Cette puissance dynamique dissipée est, évidemment, proportionnelle à la fréquence de fonctionnement, à la capacité de la charge et au carré de la tension d'alimentation. Comme le montre la figure 2, la puissance dissipée par une porte CMOS dépasse celle d'une porte Schottky faible puissance quelque part entre 500 kHz et 2 MHz de fréquence réelle de sortie.

A 100 transitions par seconde, la puissance dynamique consommée est, de loin, beaucoup plus grande que la dissipation statique et à un million de transitions par seconde, elle dépasse celle de la LS-TTL.

La comparaison de la puissance consommée par des boîtiers plus complexes (MSI) de différentes technologies peut mettre en évidence des résultats différents. Dans un boîtier complexe, seul un petit nombre de portes commutent réellement à la fréquence d'horloge, la plupart d'entre elles fonctionnent à une fréquence beaucoup plus basse et dissipent donc une puissance beaucoup plus faible.

Plage de tension d'alimentation

Le fonctionnement de la famille CMOS est garanti dans une plage sans précédent de tension d'alimentation allant de 3 à 15 V. Les caractéristiques spécifiées par le constructeur sont garanties à 5, 10 et 15 V et peuvent être extrapolées pour une tension d'alimentation quelconque comprise entre ces limites. L'utilisation du circuit à une tension inférieure à 4,5 V n'est pas très significative à cause de l'allongement du temps de propagation (perte de vitesse), l'augmentation de l'impédance de sortie et la diminution de l'immunité au bruit. Il n'est pas conseillé, non plus, d'alimenter le circuit avec une tension supérieure à 15 V à cause de l'importante puissance dynamique dissipée et le risque d'apparition, sur l'alimentation, de tensions transitoires dépassant la tension de claquage (> 20 V), provoquant un verrouillage dû au bruit et détruisant le boîtier sauf si le courant est limité extérieurement. La limite basse de la tension d'alimentation, ondulation résiduelle comprise, est fonction de l'immunité au bruit, du temps de propagation ou de l'interfaçage avec la famille TTL désirés. La limite haute de cette tension, ondulation résiduelle et transitoires comprises, est fonction de la puissance dissipée ou de l'interfaçage direct avec la TTL. Les 4049 et 4050 permettent une adaptation de niveau entre TTL et CMOS lorsque celle-ci utilise une tension d'alimentation supérieure à 5 V. Bien que les boîtiers puissent être alimentés par une tension de 18 V, il est déconseillé de dépasser 12 V à cause de la puissance dissipée.

Une faible consommation de puissance statique doublée d'une large plage de tension d'alimentation font de la CMOS la famille logique idéale pour les systèmes alimentés par piles.

Temps de propagation

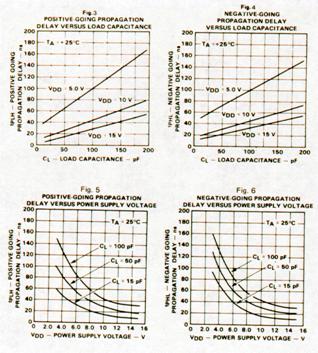

Par rapport aux familles TTL et LS-TTL, la famille CMOS est lente et très sensible aux charges capacitives. Le temps de propagation dépend de trois paramètres : la capacité de la charge, la tension d'alimentation et la température.

Influence des charges capacitives

Les figures 3 et 4 montrent les durées des transitions positives et négatives en fonction de la capacité de la charge. On pourra remarquer que les anciennes portes, non tamponnées, ont une impédance de sortie encore plus élevée, une sensibilité plus élevée à la charge et ne présentent pas la même symétrie.

Influence de la tension d'alimentation

La figure 5 montre la variation du temps de propagation en fonction de la tension d'alimentation. Elle montre encore une symétrie entre les durées des transitions positives et négatives. Si on augmente la tension d'alimentation et la faisant passer de 5 V à 10 V, la vitesse des portes CMOS est plus que doublée. Le fait d'amener cette tension à 15 V, double encore cette vitesse mais, comme nous l'avons dit plus haut, augmente d'une manière significative la dissipation de puissance dynamique.

Pour les applications à faible vitesse, 5 V est la valeur optimale de la tension d'alimentation. Pour les systèmes dont la vitesse reste raisonnable, utiliser une tension de 10 à 12 V. Pour les applications qui nécessitent une alimentation en 15 V pour des temps de propagation courts et une fréquence de fonctionnement élevée, il faudra étudier soigneusement l'intérêt de l'utilisation de la CMOS pour éviter une puissance dissipée excessive et la comparer à une approche LS-TTL.

Influence de la température

Le temps de propagation dépend de la température ambiante. L'influence de la température est plus simple avec la famille CMOS qu'avec la famille TTL où elle dépend de trois paramètres : augmentation du facteur b avec la température, augmentation de la résistance avec la température et diminution de la chute de tension directe de jonction avec l'augmentation de la température. Avec la famille CMOS, la modification essentielle est la mobilité des porteurs, ce qui augmente l'impédance et donc le temps de propagation avec la température. Pour un boîtier de la série 4000B, l'influence de la température est inférieure à 0,3% par °C et pratiquement identique dans toute la plage de température d'utilisation. Notons que la plage de température commerciale est de 40 °C à +85°C alors que la plage usuelle est de 0°C à +75°C. Le temps de propagation de la CMOS augmente avec la température. Il est très sensible à la capacité de la charge mais peut être réduit en augmentant la tension d'alimentation à 10 et même 15 V.

Immunité au bruit

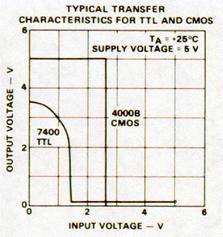

Une des qualités de la famille CMOS, dont on parle le plus mais qui est aussi la moins comprise, est l'immunité au bruit. Le seuil d'entrée d'une porte CMOS est d'environ 50% de la tension d'alimentation et la courbe de transfert en tension est quasiment idéale. Par conséquent la famille CMOS peut être considérée comme ayant une très bonne tension d'immunité au bruit, typiquement 45% de la tension d'alimentation, cest-à-dire 2,25 V pour une alimentation de 5 V et 4,5 V pour une alimentation de 10 V. On peut rapprocher cette courbe de celle de la famille TTL de la figure 7 et constater que l'immunité au bruit de celle-ci n'est que de 1 V dans le cas d'une faible charge. Immunité qui est ramenée à 0,4 V dans le pire des cas. Comme pour la famille CMOS l'impédance de sortie, la tension de sortie et seuil d'entrée sont symétriques par rapport à la tension d'alimentation, les immunités au bruit au niveau logique haut et au niveau logique bas sont pratiquement égales. Par conséquent, un système à base de circuits CMOS peut accepter des pointes de tension et du bruit sur ces lignes d'alimentation positive et négative de plus de 1 V d'amplitude, même s'il est alimenté en 5 V. De plus, le temps de propagation inhérent à la technologie CMOS se comporte comme un filtre de bruit. Des pointes de 10 ns tendent à disparaître dans une chaîne de portes CMOS mais sont amplifiées dans une chaîne de portes TTL. A cause de ces propriétés, la famille CMOS est très appréciée des fabricants d'équipements de commande industriels qui doivent fonctionner dans un environnement électriquement et électromagnétiquement pollué.

Malheureusement ces caractéristiques d'immunité au bruit spectaculaires ne tiennent pas compte d'un fait important : l'impédance de sortie d'un circuit CMOS est de 10 à 100 fois plus élevée que celle d'un circuit TTL. Les interconnexions entre CMOS sont, par conséquent, moins raides et beaucoup plus sensibles au bruit par couplage capacitif. Dans le cas de courants provenant de tensions de bruit élevées et injectés dans de petites capacités de couplage, la famille CMOS tolère une marge de bruit environ six fois plus faible que la famille TTL. Il faut plus de 20 mA pour amener une sortie dans la zone de déclenchement mais seulement 3 mA pour une sortie CMOS dans un système alimenté en 5 V.

La caractéristique de transfert presque idéale et le temps de réponse lent des circuits CMOS les rendent insensibles aux faibles tensions de bruit par couplage magnétique. Leur impédance de sortie élevée leur donne cependant une mauvaise réjection du bruit par couplage capacitif.

Interfaçage avec la famille TTL

L'interfaçage avec la famille TTL est direct lorsque les circuits CMOS sont alimentés en 5 V. L'impédance d'entrée de ces circuits étant très élevée, les circuits CMOS peuvent être commandés par n'importe quel type de TTL sans perte de sortance au niveau logique bas. Malheureusement, la plupart des types de TTL ont une tension insuffisante au niveau logique haut (3,5 V typiques) pour commander la famille CMOS en toute sécurité. On pourra relever la tension du niveau logique haut du circuit TTL à 4,5 V (ou plus) en connectant une résistance de rappel (1 kW à 10 kW) entre la sortie du circuit TTL et le potentiel positif de la tension d'alimentation.

L'interfaçage direct est impossible lorsque le circuit CMOS est alimenté par une tension supérieure à 5 V. Les sextuples tampons 4049 et 4050 peuvent être commandés par des niveaux logiques issus de circuits CMOS alimentés par une tension de plus de 15 V et peuvent, eux-mêmes, commander deux charges standard TTL.

Capacités d'entrée et de sortie

Les circuits CMOS ont une capacité d'entrée comprise entre 1,5 et 5 pF et une capacité de sortie comprise entre 3 et 7 pF.

Protection des entrées

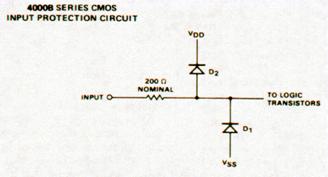

L'entrée sur la porte d'un transistor MOS est assimilable à un petit condensateur (< 1 pF) à très faible courant de fuite (< 10 nA). Si on ne prend aucune précaution spéciale, cette entrée peut se charger à une tension électrostatique élevée, ce qui provoque un claquage destructeur du diélectrique et une avarie irréversible du circuit. Par conséquent, toute entrée CMOS est protégée par un réseau de résistances série et de diodes en court-circuit. Les différents fabricants ont utilisé des techniques variées : certains n'utilisent qu'une seule diode, d'autres deux et d'autres enfin une résistance et une diode parasite du substrat.

Les membres de la famille Fairchild 4000B utilisent une résistance série de 200 W et deux diodes, l'une reliée à VDD et l'autre à VSS (figure 8). La résistance est au polysilicium sans diode parasite du substrat. L'impédance d'entrée minimale est donc fixée à 200 W quelles que soient les conditions de polarisation et même si VDD et VSS sont court-circuités. Une diode parasite de substrat représenterait un shunt à VSS de mauvaise qualité dans ce cas précis.

La chute de tension directe des diodes est de 0,9 V typique et leur tension de claquage inverse est de 20 V pour D1 et D2. Dans certaines applications spéciales telles que les oscillateurs, les diodes conduisent réellement en fonctionnement normal. Cependant les courants doivent être limités à 10 mA.

Précautions à prendre dans la manipulation des boîtiers CMOS

Tous les circuits MOS risquent d'être détériorés par des décharges électrostatiques importantes. Tous les boîtiers Fairchild 4000B utilisent le circuit de protection d'entrée décrit à la figure 8. Cependant, des accidents électrostatiques peuvent encore se produire.

Il faut respecter les précautions de manipulations suivantes :

1. Les broches des circuits CMOS doivent être en contact avec une surface conductrice reliée à la masse. Les feuilles d'aluminium du commerce conviennent très bien. En aucun cas, il ne faut ranger ces circuits dans de la mousse polystyrène ou dans des rails en plastique utilisés pour le conditionnement et la manutention des circuits intégrés conventionnels.

2. Ne pas insérer ou retirer un circuit sous tension. Il faut s'assurer que les variations transitoires de la tension d'alimentation, telles que celles qui se produisent à la mise sous tension ou hors tension, n'excèdent pas les limites spécifiées.

3. Dans le montage lui-même, toutes les entrées non utilisées doivent être connectées à un niveau logique haut ou bas tel que VSS, VDD ou à la sortie d'un élément logique.

Comparaison CMOS -TTL

Le passage des circuits TTL aux circuits CMOS est généralement une transition facile et permet à l'utilisateur d'oublier beaucoup de contraintes pour bénéficier de facilités nouvelles. Citons-en quelques unes :

Sortance :

Elle est pratiquement illimitée du point de vue courant et n'est limitée que par des considérations de temps de propagation et d'établissement.

Régulation de la tension d'alimentation :

N'importe quelle valeur entre 3 et 15 V convient à la condition que tous les autres circuits soient alimentables par la même tension.

Chute de tension dans les lignes d'alimentation :

Les courants sont normalement si faibles qu'il n'est pas nécessaire d'utiliser des lignes d'alimentation générales de dimensions particulières.

Découplage de l'alimentation :

Il peut être réduit à quelques condensateurs par carte.

Problèmes d'échauffement :

Ils n'existent pas sauf si on essaie de faire fonctionner la CMOS à grande vitesse ou sous une tension d'alimentation supérieure à 10 V.

Il faut dire également que l'utilisation des CMOS appelle certaines précautions et les principes de base ne doivent être oubliés. Citons quelques unes des nouvelles règles d'utilisation :

Entrées non utilisées :

Elles doivent être connectées à VSS ou à VDD (à VCC ou à la masse) de peur qu'elles ne produisent un peut-être logique. La mauvaise habitude de laisser en l'air les entrées TTL non utilisées est à bannir définitivement.

Oscillations :

Les signaux d'entrée à variation lente peuvent amener des oscillations et des déclenchements multiples. Une tension d'alimentation mal régulée et mal découplée augmente ce risque puisque le seuil d'entrée CMOS varie avec la tension d'alimentation.

Détails de séquencement :

Même pour les systèmes lents, il est conseillé d'analyser avec soin les temps de propagation pris dans le pire des cas, à température maximale, tension d'alimentation minimale et capacité de la charge maximale. Beaucoup de bascules CMOS, registres et verrous ont un temps de maintien minimal réel ce qui veut dire que les entrées doivent rester stables même après le flanc actif d'horloge ; d'autres nécessitent un temps de montée minimal du signal d'horloge. Ce n'était pas un problème avec la TTL. Les systèmes à CMOS, même lents, sont prédisposés à être victimes de problèmes insoupçonnés de recouvrement de signaux d'horloge puisqu'un générateur d'horloge lourdement chargé peut avoir un mauvais temps de montée.

Compatibilité :

L'utilisateur des circuits TTL sait que les circuits, vendus par différents fabricants sous le même numéro de référence, sont pratiquement identiques électriquement. Beaucoup de constructeurs livrent des boîtiers de type 4000 présentant de grandes variations de sortance et de vitesse.