L'interface série le 8250/16550

I ) Introduction :

Malgré sa rapidité la liaison parallèle n'est pas adapter à quelque application lors de la communication entre le microprocesseur et ses périphériques, en effet ce type de liaison a des faiblesses lorsqu'il s'agit de communiquer avec un organe pour une longue distance, à cet effet on préfère utiliser la liaison série malgré son faible débit contre la liaison parallèle.

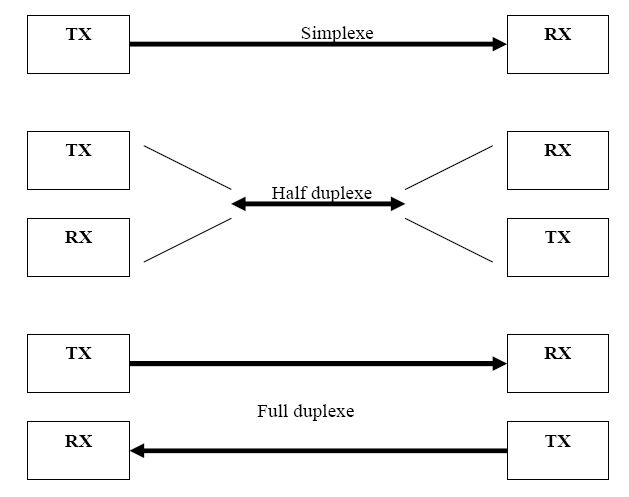

La liaison entre l'émetteur et le récepteur en mode série peut être :

- Simplexe.

- Half duplexe

- Full duplexe

La figure suivante montre la différence entre les trois modes :

TX : ligne d'émission. RX : ligne de réception.

Remarque :

La vitesse de transmission est mesurée en bps (bits par seconde), mais aussi BAUD (nombre des changements du signal par Seconde). Il existe 2 types de Communications Série: Synchrone et Asynchrone :

I-1 ) Communications asynchrones

Ici la transmission s'effectue caractère par caractère.

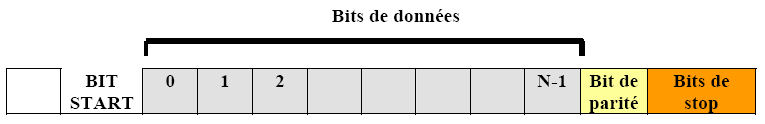

Un caractère comprend :

- un bit de départ (START),

- des bits de donnée selon un format variable (5, 6, 7,8 bits),

- un bit de parité (optionnel),

- un ou plusieurs bits d'arrêt (Stop).

La cadence de transmission est fixée par une horloge dont la période donne le temps de transmission de 1 bit.

Au repos, la ligne de transmission est à l'état 1. Le début de transmission est signalé par l'apparition du bit de départ qui est dans l'état logique 0 (START). Les bits de donnée sont ensuite transmis séquentiellement. Un bit de parité est ajouté éventuellement à la suite des bits de donnée pour vérifier la bonne transmission des données en effet il permet de détecter des erreurs de transmission. La fin de transmission du caractère est signalée par un ou plusieurs bits d'arrêt à l'état 1 (bits STOP). Le bit de départ permet au récepteur de détecter l'arrivée d'un caractère et de recaler la phase de l'horloge de réception afin d'échantillonner correctement les bits suivants (au milieu de chacun des bits). Ainsi, comme les fréquences d'émission et de réception ne sont pas strictement identiques, il suffit de garantir une précision de quelques pour-cent pour assurer une réception valide. Les vitesses normalisées sont : 50, 75, 110, 150, 300, 600, 1200, 2400,4800, 9600, 19200, 38400 bauds.

I-2 ) Communication synchrone :

Avec la communication synchrone les données sont transmissent d'une manière continue. Il est donc nécessaire d'effectuer la synchronisation des caractères au début du bloc de données. Cette synchronisation peut être interne ou externe :

- La synchronisation interne : le récepteur détecte un ou plusieurs caractères de synchronisation en tête de message, en cherchant une correspondance bit à bit entre un caractère de synchronisation préétabli et le train de bits arrivant.

- La synchronisation externe : nécessite une ligne spécialisée qui fournit un top d'horloge à chaque début de transmission de bloc.

Remarque 1 :

Dans tous les cas, une horloge cadence la transmission des bits qui ne sont donc émis qu'à des instants déterminés.

Remarque 2 :

Il existe deux circuits pour les Communications Série: UART (Universal Asynchrenous Receiver-Transmitter, (les Ports COM d'IBM PC utilisent l'UART8050/16550 de NS ) et USART (Universal Synchroneous- Asynchroneous Receiver-Transmitter (Le 8251 de Intel).

II ) L'interface série le 8250/16550 :

II-1 ) Introduction :

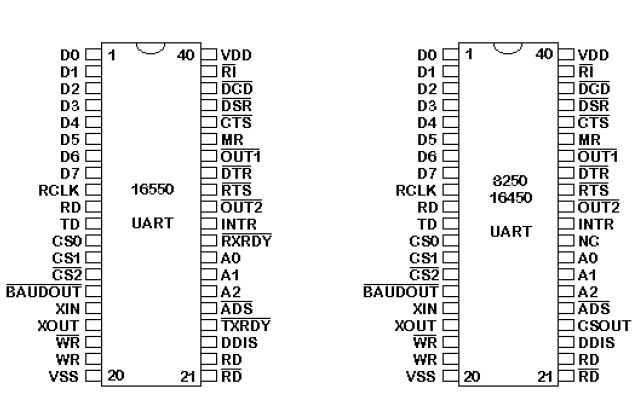

Le composant électronique chargé de la gestion des transmissions séries asynchrones dans les PC est appelé UART (Universal Asynchronous Receiver Transmitter).le circuit qui gère cette communication est le 8250 de National Semiconductor ou son équivalent le 16550 dont le brochage est comme suit :

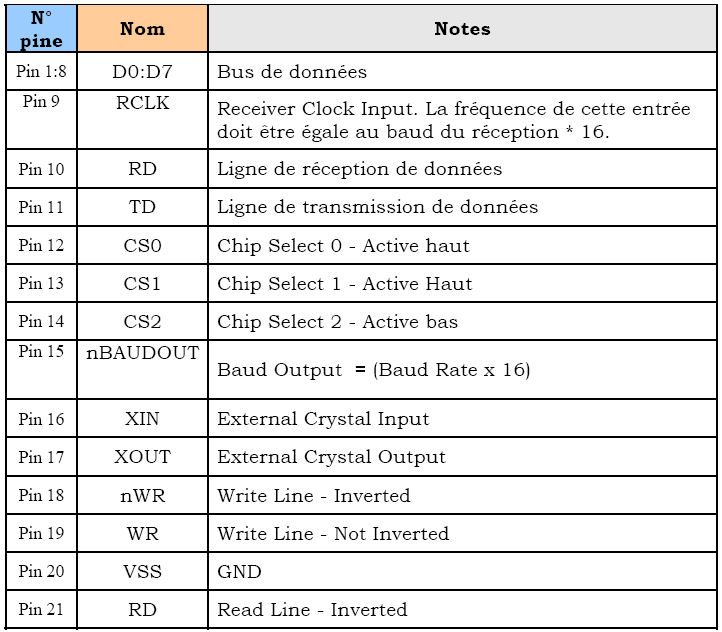

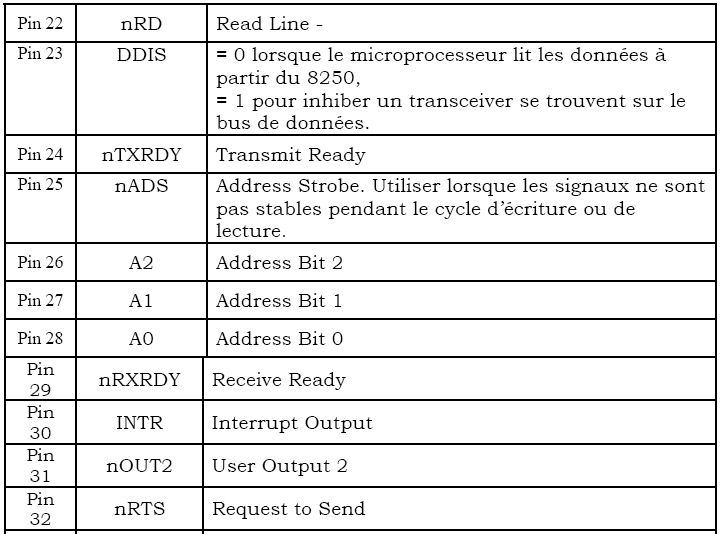

II-2 ) Description des pines :

III ) Les registres du 8250 :

III-1 /Les registres de contrôle de protocole

Ces registres permettent de construire un protocole sommaire (réglages des bits de parités et de stop, sélection de la vitesse de transmission) :

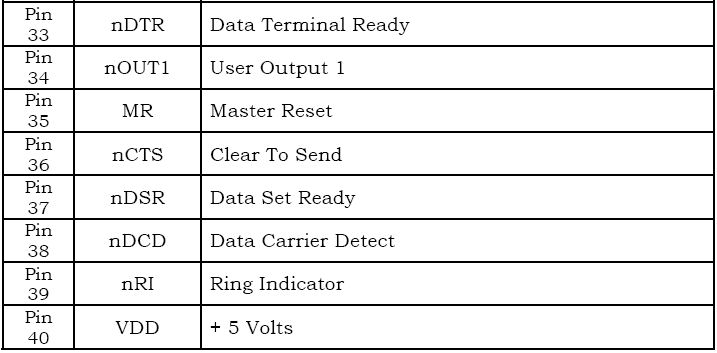

III-1-1 ) LCR - Line Control Register (registre de contrôle de la ligne)

III- 1- 2 ) DLR - Divisor Latch Register (registre de sélection de la vitesse de transfert)

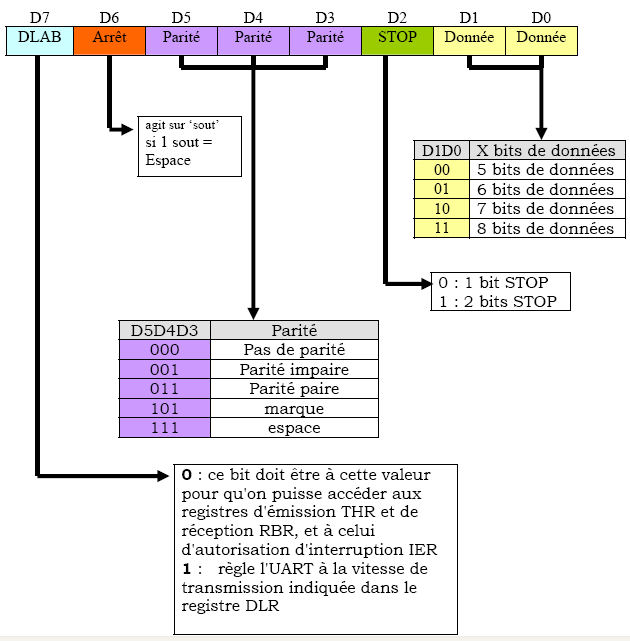

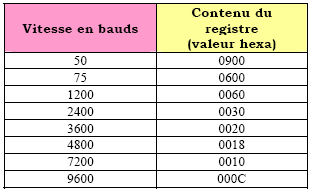

ce registre est codé sur 16 bits : Pour pouvoir utiliser ce registre on a deux adresses, qui permetent de sélectionner facilement une vitesse de transfert de 50 à 9600 bauds (c'est à dire un maximum de 19200 bps), mais il ne faut pas oublier auparavant de forcer le bit DLAB du registre LCR à l'état 1.

Remarque :

La vitesse n'est pas programmée directement dans l'UART - c'est un circuit comparable à une horloge (baud rate generator) qui se charge de réguler celle-ci.

EXEMPLE : pour régler l'UART à une vitesse de 9600 bauds, il faudra copier 0x0C vers DLR.

III - 2 ) Les registres de contrôle de la ligne

Ils sont au nombre de trois, et permettent de connaître l'état de la ligne ou du modem, et de réinitialiser celui-ci :

III - 2 - 1 ) LSR - Line Status Register (registre d'état de la ligne)

- DR (Data Received) : Si DR =1, ce bit indique qu'un caractère complètement transmis se trouve dans le registre de réception RBR. La lecture de celui-ci réinitialisera automatiquement ce bit DR à 0.

- OR (OverRun) : ce bit est mis à 1 quant le registre de réception RBR n'est pas vide et qu'une donnée reçue risque d'écraser son contenu. Une simple lecture du registre de LSR réinitialisera ce bit à 0.

- PE (Parity Error) : mis à 1 sur une erreur de parité. Réinitialisé à la lecture de LSR.

- FE (Frame Error) : bits de stop incorrects. Reste à 1 tant que le premier bit de stop (celui suivant le dernier bit de données ou le bit de parité) est à 0.

- BE (Break Interrupt) : erreur de type break sur la ligne

- THR (Transmission Holding Register Empty) : ce bit prend la valeur de 1 quand l'UART a fini de transmettre le dernier caractère du registre de transmission THR dans le registre TDR.

- TSRE (Transmitter Shift Register Empty) : ce bit est en lecture seule. Il indique (passage à l'état 1) que le caractère du registre TDR a été envoyé sur la ligne, et donc que celui-ci est vide. Dès qu'une donnée arrive de THR dans TDR, la valeur repasse à 0.

III-2-2 ) MSR - Modem Status Register (registre d'état du modem)

Les valeurs de ce registre correspondent aux broches de l'interface. Les bits 0 à 3 indiquent les variations depuis la dernière lecture du processeur du registre - ils seront forcés à 1 si il y a eu changement. Toutes leurs valeurs sont réinitialisées, s'il y a lieu, à un 0 logique dès que le processeur a achevé une lecture du registre. Les bits 4 à 7 contiennent, quant à eux, l'état actuel de diverses données de la ligne.

- DCTS (Delta Clear To Send) : variation d'état de la broche CTS (préparation d'émission)

- DDSR (Delta Data Set Ready) : variation d'état de la broche DSR (données prêtes)

- TERI (Trailing Edge of Ring Indicator) : entrée RI de l'UART (Ring Indicator). Ce bit passe à 1 si RI passe de ON (0) à OFF (1). Un appel a été détecté depuis la dernière lecture.

- DRLSD (Delta Received Line Signal Detector) : variation d'état de l'entrée RLSD de l'UART. Indique si la liaison avec le modem distant a été établie.

- CTS (Clear To Send) : état de la broche CTS.

- DSR (Data Set Ready) : état de la broche DSR.

- RI (Ring Indicator) : signale un appel sur la ligne.

- RLSD (Receive Line Signal Detect) : indique si la liaison avec le modem distant a été établie.

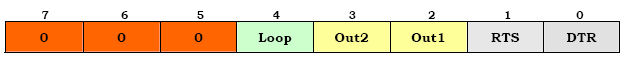

III-2-3 ) MCR - Modem Control Register (registre de contrôle du modem)

Les bits OUT1, OUT2, RTS et DTR permettent, en forçant leur valeur, de contrôler la valeur barre des signaux correspondants (DTR et RTS correspondent à des broches de l'interface, OUT1 et OUT2 sont des sorties auxiliaires).

III- 3 ) Les registres de contrôle d'interruptions

On pourra par le biais de ces registres déclarer quels événements déclencheront une interruption. Une fois l'interruption détectée dans le programme, on pourra définir sa cause, et y répondre.

III - 3 - 1 ) IER - Interrupt Enable Register (registre d'autorisations d'interruptions) :

Le bit DLAB du registre LCR (registre de contrôle de ligne) doit être forcé à 0 pour pouvoir accéder à ce registre. Les quatre bits de poids faible (bits 0 à 3) permettent, lorsqu'ils sont forcés à 1, de générer une interruptions lors de l'apparition de l'événement associé - on pourra retrouver la cause de cette interruption dans le registre IIR. La liste ci-dessous définit quels événements associés avec les bits de ce registre :

- EDAI (Enable Data Available Interrupt) : arrivée d'un caractère

- ETHREI (Enable Tx Holding Register Empty Interrupt) : registre THR vide

- ERLSI (Enable Receive Line Status Interrupt) : modification de l'état de la ligne

- EMSI (Enable Modem Status Interrupt) : modification de l'état du modem

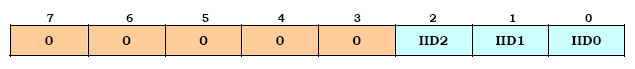

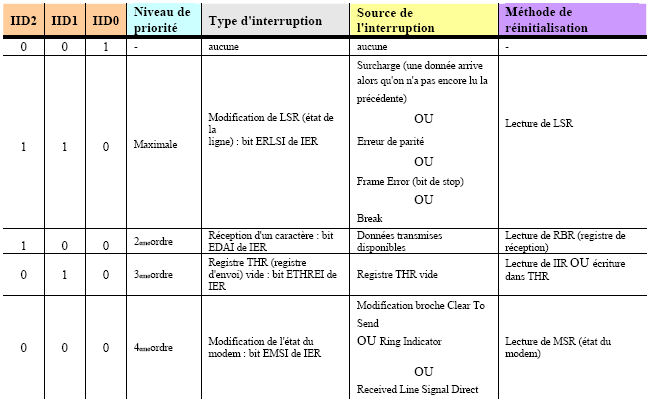

III-3-2 / IIR - Interrupt Identification Register (registre de cause d'interruption)

Les trois bits IID (Interrupt ID) permettent de connaître la cause de l'interruption, sa priorité, et le moyen de désactiver l'interruption. Le tableau suivant fournit la liste des combinaisons de ces trois bits et leur signification :

III-4 ) Les registres de transfert

III-4-1 ) Les registres d'émission

Lorsqu'un caractère doit être transmis, il doit d'abord être transféré dans le registre THR (Transmission Holding Register = registre d'attente de l'émetteur). Il y restera tant que le caractère précédent ne sera pas acquitté par la machine distante. Une fois l'acquittement reçu, le caractère sera transféré dans un autre registre :

TSR (Transmission Shift Register = Registre de décalage de l'émetteur). L'UART se chargera alors de transmettre le caractère bit à bit sur la ligne, et il pourra y insérer, selon les réglages effectués dans LCR (contrôle de ligne), un bit de parité et un nombre fixé de bits de stop. Il est important de noter ces quelques remarques :

· Ce registre est à écriture seule (il possède la même adresse que RBR, le registre de réception : un ordre de lecture à l'adresse de THR renverra donc le contenu de RBR)

· Le bit DLAB du registre LCR (contrôle de la ligne) doit être forcé à 0 pour pouvoir effectuer une écriture dans ce registre.

· Ce registre est sur 8 bits. On pourra y envoyer de 5 à 8 bits, suivant les réglages du registre de contrôle de ligne LCR (bits WLS), sachant que ce sera le bit 0 (poids le plus faible) qui sera le premier transmis.

· il sera judicieux d'effectuer une lecture de LSR (registre d'état de la ligne) - bits 5 et 6 - pour savoir quand le registre THR devient libre, et quand le caractère présent dans TDR a été transmi totalement sur la ligne .

III-4 - 2 ) Les registres de réception

L'octet reçu sera transféré (sans ses bits de parité et de stop) dans le registre RBR (Receiver Buffer Register = registre de réception). De la même manière qu'avec les registres d'émission, il existe un registre de transit - appelé RDR - par lequel le bit reçu passera en premier, avant d'être débarrassé de ses bits de contrôle.

Remarque :

· Le registre RBR est à lecture seule. les registres d'émission THR et de réception RBR possèdent une adresse commune. Ainsi une écriture sur l'adresse de RBR provoquera un remplissage du registre THR, et n'aura aucun effet sur le registre de réception.

· Le bit DLAB du registre LCR (contrôle de la ligne) doit être forcé à 0 pour pouvoir effectuer une lecture dans ce registre.

· Ce registre est sur 8 bits : y seront copiés les 5 à 8 bits de données, sans bits de contrôle. Le bit 0, de poids le plus faible, est le premier à avoir été reçu.

· il sera judicieux d'effectuer une lecture de LSR (registre d'état de la ligne) - bits 0 à 4 - pour détecter les éventuelles erreurs de transmission, ou tout simplement pour savoir si un caractère a été reçu-se reporter à la partie traitant de ce registre.

IV Exemple de programmation du 8250/16550 :

IV-1 ) Programmation directe :

Exemple de programme qui permet de lire un caractère du port COM1 par polling :

LSR EQU 3FDH TXRX EQU 3F8H RDA EQU 01H TBE EQU 20H DEBUT : IN AL, LSR ; Lecture de LSR TEST AL, RDA ; tester RDA JZ DEBUT ; if not RDA IN AL, TXRX ; lecture de la donnée

EXAMPLE 2: Ecriture d'un caractère sur le port COM1 :

DEBUT : IN AL, LSR ; Lecture LSR TEST AL, TBE ; tester TBE JZ DEBUT MOV AL, 'a' ; caractère à transmettre OUT TXRX, AL ; envoie caractère sur le portIV-2 ) Programmation en utilisant les interruptions BIOS/ DOS :

L'interruption 21H (DOS):

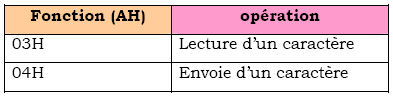

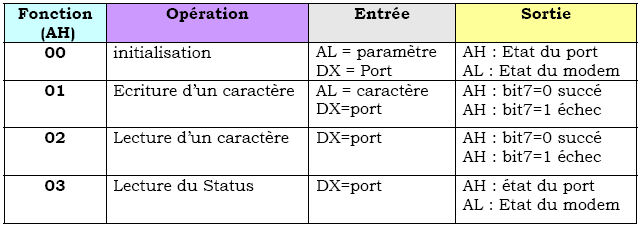

L'interruption BIOS 14H :

Exemple de programme Ecriture d'un mot :

COM1 EQU 0 COM2 EQU 1 TBE EQU 20H RDA EQU 01H DEBUT :MOV DX, COM1 MOV AH, 03H INT 14H TEST AH, TBE ; test la valeur de TBE JZ DEBUT MOV DX, COM1 MOV AH, 01H MOV AL, 'a' ; Ecriture du caractère INT 14HExemple de programme de lecture d'un caractère :

COM1 EQU 0 COM2 EQU 1 TBE EQU 20H RDA EQU 01H DEBUT: MOV DX, COM1 MOV AH, 03H INT 14H TEST AH, RDA JZ DEBUT MOV DX, COM1 MOV AH, 02H INT 14H