Une FPGA qui perce les limites de la loi de Moore en densité et bande passante

| Catégorie : Electronique | Ajouté le : 28/10/2010 20:01 |

| Ajouté par : Technologuepro | Lectures : 18662 |

| Commentaires : 0 [ Poster un commentaire ] | Note : Non évalué |

|

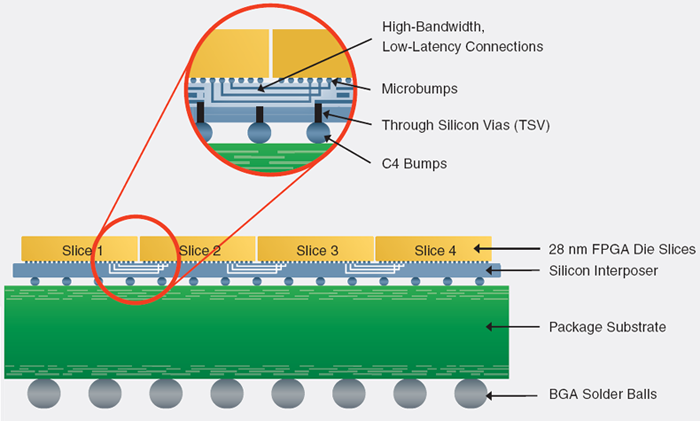

La nouvelle technologie d'interconnexion en silicium empilés (Stacked silicon interconnect technology) offre une amélioration de 100x en bande passante et une capacité 2 à 3x par rapport aux dispositifs monolithiques. La technologie fournit les ressources nécessaires dans une FPGA pour concevoir des applications qui nécessitent des capacités de calcul très élevées et des performances très haute comme par exemple : les processeurs embarqués, la prochaine génération de communications filaires ou sans fil et le traitement d'images médicales...

Xilinx a développé une approche novatrice pour la conception et la fabrication des FPGA qui répond aux exigences de l'électronique programmable de nos jours et dans le futur. La technologie d'interconnexion en silicium empilés (Stacked silicon interconnect technology) est le fondement d'une nouvelle génération de FPGA qui perce les limites de La loi de Moore Les circuits FPGA devient de plus en plus importants dans la conception des systèmes, les modèles deviennent de plus en plus gros et complexes, exigeant une plus grande capacité logique et plus de ressources sur la puce. À ce jour, les FPGA ont suivit parfaitement la loi de Moore pour répondre à ce besoin, en apportant entre 1.5 et 2 fois la capacité logique à chaque nouvelle génération de circuit. Pour surmonter ces limitations, Xilinx a développé une nouvelle approche pour la construction des des FPGAs. La nouvelle solution permet une connectivité à haut débit entre plusieurs dies en fournissant un plus grand nombre de connexions. Elle impose aussi des temps de latence beaucoup plus faible et consomme beaucoup plus moins de l'énergie que l'approche multiple FPGA, tout en permettant l'intégration de quantités massives d'interconnexion logique et des ressources sur puce dans un seul paquet.

Un des avantages les plus substantiels offert par les FPGA Xilinx avec la technologie d'interconnexion en silicium empilés (Stacked silicon interconnect technology) est la possibilité de la considérer comme un dispositif monolithique (FPGAs classiques). Cela est extrêmement important parce qu’un système à plusieurs FPGA présente un certain nombre de défis de conception complexes que les implémentations monolithique évitent entièrement. Les étapes typiques dans une conception sur une FPGA monolithique sont:

Lorsqu’il travaille avec plusieurs FPGA, le concepteur doit générer de multiples netlists. Donc travailler avec plusieurs projets, chacun avec sa propre conception de fichiers, bibliothèques IP, assignation physique, information sur les temps de propagation, etc. La conception avec plusieurs FPGA peut être extrêmement difficile. Calculer et accueillir des retards de propagation à travers les différents projets. De même, le débogage d'une conception à multiples FPGA peut être extrêmement compliqué et difficile. En revanche, avec la nouvelle technologie d'interconnexion en silicium empilés (Stacked silicon interconnect technology), le concepteur crée et gère un projet de conception unique. Source Xilinx octobre 2010 | |

Lectures recommandées sur ce thème :

Cours

Cours Circuits Logiques Programmables (FPGA, DSP) - Catégorie :

Projets fin d'études

Application à base des circuits FPGA - (07/07/2013)

Articles

Nios II, le processeur embarqué d'Altera annonce une nouvelle aire pour l'électronique - (08/10/2010)

Altera livre ses FPGA Arria II GX avec transceiver en 40 nm - (10/06/2009)

Séminaire de l'Electronique et de l'Informatique Industrielle (SEII2009) - (25/02/2009)

Altera présente les premiers FPGA et ASIC HardCopy. - (15/08/2008)

Les circuits logiques programmables FPGA ! - (12/04/2008)

Téléchargements

Guide d'utilisation de XILINX ISE 9.2i - (12/05/2008)

Annuaire

GENELAIX - (10/07/2013)

Xilinx FPGA et CPLD - (11/08/2013)

Altera FPGA, CPLD et ASIC - (11/08/2013)

Forums

PFE - (15/02/2012)

salut - (21/04/2011)

aide implantation de methode SOM de reseaux de neurone sur FPGA - (31/03/2011)

comparaison entre l'architecture d'altera et architecture d'xilinx - (14/03/2010)

HDL :langage et logiciels que je doit choisir pour bien débuter FPGA - (06/07/2009)

Commentaires

Aucun commentaire dans la base de données