Contrôle des cartes électroniques par la méthode Boundary Scan (JTAG)

1 - Introduction

La technique de Boundary-Scan (scrutation des frontières) est conçue pour faciliter et automatiser le test des cartes électroniques numériques. Elle consiste à donner un accès auxiliaire aux broches d'entrée-sortie des composants numériques fortement intégrés.

Le JTAG pour Joint Test Action Group est le nom de la norme IEEE 1149.1 intitulé « Standard Test Access Port and Boundary-Scan Architecture ». Le JTAG a été normalisé en 1990. Le terme JTAG, désignant le groupe de travail qui a conçu la norme, est abusivement (mais très largement) utilisé au lieu du terme générique Boundary Scan, ou du sigle TAP (Test Access Port, port d'accès de test).

2 - Principe

Initialement, le Boundary Scan était uniquement destiné au test des court-circuit et de la continuité entre puces compatibles. Connaissant le schéma électrique de la carte électronique, on applique un ensemble de signaux logiques (appelé vecteur de test) sur les broches d'entrée de certains composants (depuis la chaîne Boundary Scan interne), et on relève les niveaux logiques sur les broches de sortie des composants qui y sont connectés, pour s'assurer qu'ils correspondent aux valeurs attendues. On peut ainsi s'assurer de la bonne qualité des pistes du circuit imprimé et des soudures.

Pour cela, chaque broche d'entrée-sortie n'est pas connectée directement à l'intérieur du composant numérique, mais à travers une « cellule JTAG » permettant de la piloter indépendamment de sa fonction initiale. Il est ainsi possible de la configurer en entrée (haute-impédance) ou en sortie (niveau logique haut ou bas).

Figure 5.1 : Schéma block d’une chaine JITAG typique

Cependant chaque type de broche a un nombre de cellules qui lui est associé. Les broches d'entrée et de sortie n'ont besoin que d'une cellule chacune. Les broches tristates ayant besoin de deux entrées pour fonctionner (entrée de signal et activation de l'état haute impédance), il faudra donc deux cellules pour pouvoir les tester.

Les broches I/O (pour Input/Output, ou encore Entrée/Sortie) sont quant à elles composées d'une sortie ainsi que d'une entrée qui peut être placée en haute impédance. Étant donné ce qui a été dit précédemment, pour mettre à l'état haute impédance, il y a besoin de deux cellules. Il faudra donc en tout pas moins de trois cellules pour pouvoir tester une broche I/O.

Figure 5.2 : chaîne Boundary Scan interne

Il est à noter que les cellules ne sont pas utilisées pour tester les broches d'alimentation, d'horloge et de reset. Les cellules sont connectées entre elles par un bus série faisant le tour de la puce (d'où la notion de « frontière » ou Boundary), équivalent à un grand registre à décalage de taille égale ou supérieure au nombre de broches d'entrée-sortie du composant.

On appelle ce registre BSR, pour Boundary Scan Register. Le TAP Controller, qui reçoit les signaux JTAG de l'extérieur, permet d'activer et de piloter les cellules selon une séquence normalisée.

3. Applications

Le JTAG n'est pas limité aux tests de continuité. Il est en effet également possible de tester (au moins partiellement) des fonctions logiques combinatoires, même si elles sont composées de puces non compatibles JTAG, en élaborant des vecteurs de test appropriés et à condition que les entrées et sorties de ces fonctions soient connectées à des composants JTAG.

De même, il est possible de tester des mémoires en écrivant puis relisant des valeurs de test. Il est même possible de cette manière de programmer des mémoires non-volatiles (EEPROM et Flash, ces dernières nécessitant un protocole particulier).

De plus, le JTAG n'est pas limité aux connexions externes au composant. La norme JTAG est ainsi utilisée pour remplacer les émulateurs de microprocesseurs (systèmes de débug sur carte remplaçant physiquement le composant), en donnant un accès direct à l'intérieur du processeur (points d'arrêt, lecture et écriture des registres internes, des mémoires internes et externes …) sans perturber ses interactions avec l'extérieur. On nomme cette technique ICE (In-Circuit Emulator) ou ICD (In-Circuit Debugger), et elle est omniprésente sur les microprocesseurs et microcontrôleurs modernes.

Le bus JTAG est également utilisé pour programmer les composants logiques programmables (FPGA et CPLD) ainsi que de nombreux microcontrôleurs (grâce à la capacité du JTAG de programmer la Flash des microcontrôleurs.), voire pour débugger un microprocesseur ou accéder à un « analyseur logique » intégrés dans un FPGA.

4. Architecture JTAG

Chaque signal primaire d’entrée et de sortie est complété avec un élément de mémoire appelé cellule Boundary-Scan. Les cellules qui agissent sur les composants JTAG d’entrée sont notées cellules d’entrée, de même que les cellules qui agissent sur les composants JTAG de sortie sont notées cellules de sortie.

Entrées et sorties sont des notations relatives au noyau logique du composant (nous verrons par la suite les problèmes que peut entraîner le fait de noter entrées et sorties les interconnections entre deux ou plusieurs composants JTAG).

Figure 5.3 : cellule Boundary-Scan

Le regroupement de cellules Boundary-Scan est configuré dans un registre à décalage d’entrée/sortie.

Une opération de chargement parallèle appelée ‘capture’ permet de charger les données en entrée du composant JTAG vers l’entrée des cellules JTAG. En même temps, elle prend la valeur du noyau logique et la transfère vers la sortie du composant JTAG pour être ensuite chargée vers l’entrée de la cellule JTAG. Elle permet donc de charger la totalité des données à l’entrée des cellules JTAG.

Une opération de déchargement appelée ‘update’ va décharger la valeur à l’entrée de la cellule JTAG vers le noyau logique. Une opération ‘update’ va donc suivre une opération ‘capture’. Ces valeurs de remplacement à l’entrée du composant JTAG et du signal déjà présent à la sortie de la cellule JTAG sont donc transférées vers la sortie du composant JTAG, remplaçant ainsi la valeur de sortie générée par le noyau logique.

Les données sont donc modifiées autour du registre à décalage, dans un mode série, à partir du ‘Test Data In’ (TDI) et terminé par le ‘Test Data Out' (TDO). Le 'Test Clock' (TCK) est alimenté par un autre circuit dédié à cette tâche. Le mode de fonctionnement est contrôlé par le signal de contrôle série : le ‘Test Mode Select‘ (TMS).

5. Le chemin de scan

Le test JTAG n’influe en rien sur la fonctionnalité du noyau logique. En fait, le chemin du Boundary-Scan est indépendant de la fonction du composant. Nous allons par un exemple simple expliquer comment le chemin de scan fonctionne.

Figure 5.4 : Exemple de carte contenant quatre composants JTAG

La figure 5.4 montre une carte contenant quatre composants JTAG. Notons qu’il existe sur la carte un connecteur en entrée nommé TDI connecté sur l’entrée TDI du premier composant. Le TDO du premier composant est relié au TDI du second composant. Et ainsi de suite jusqu’à la sortie du dernier composant appelée TDO. Les TCK et TMS sont reliées à chacun des composants en parallèle.

Dans ce chemin, certains tests particuliers peuvent être appliqués à chacun des composants par l’intermédiaire du chemin de scan global. Ainsi il va être possible de charger une valeur spécifique dans les cellules JTAG d'entrées via la broche TDI de la carte (opération de décalage d’entrée), d’appliquer cette valeur au composant (opération update), de mémoriser la réponse du composant (opération capture), et de sortir cette valeur sur la broche TDO de la carte (opération décalage de sortie). En fait les cellules JTAG peuvent donc être considérées comme des clous virtuels.

Figure 5.5 : cellule JTAG universelle

Notons qu’il s’agit ici d’un exemple de réalisation d’une cellule universelle JTAG puisque le standard IEEE 1149.1 n’impose pas le schéma de cette cellule mais uniquement son fonctionnement.

Elle contient les quatre modes opératoires cités précédemment :

· Normal

· Update

· Capture

· décalage série

L’élément de mémoire est caractérisé par une bascule D précédée et suivie d’un multiplexeur.

ü En mode ‘normal’, les données introduites en entrée se retrouvent directement en sortie.

ü En mode ‘update’, le contenu du registre de sortie est transféré en sortie.

ü En mode ‘capture’, le signal de données d’entrée est routé vers le registre à décalage et la valeur est mémorisée par l’horloge DR (ClockDR) suivante.

ü En mode ‘décalage’, le Scan_Out d’un registre à bascule est directement transféré au suivant.

Il est important de noter que ni le mode capture ni le mode décalage n’interfèrent avec le mode normal. Ceci permet de mémoriser la valeur d’une opération et de l’appliquer où l’utilisateur le désire pour une éventuelle inspection sans engendrer aucune interférence. Cette application de l’architecture JTAG a d’énormes potentiels pour des ‘monitorings’ en temps réels.

La méthode de test JTAG, comme nous l’avons indiqué précédemment, est définie par le standard IEEE 1149.1. Voyons précisément ce que cette norme impose.

6. Architecture d’un composant à la norme IEEE 1149.1

Après cinq ans de discussions, l’organisation JTAG a finalement proposé une architecture telle que le montre la figure 5.6 :

Figure 5.6 : architecture JTAG

Cette figure montre les éléments suivants :

- Les quatre broches de test : Test Data In (TDI), Test Mode Select (TMS), Test Clock (TCK), Test Data Out (TDO), une broche optionnelle : le Test Reset (TRST*).

- Les regroupements de toutes ces broches forment le Test Access Port (TAP).

- Une cellule JTAG de chacune des broches d’entrées et de sortie du composant est reliée de manière interne à un registre Boundary-Scan série.

- Une machine d’état qui contrôle le TAP par l’intermédiaire du TCK et du TMS.

- Un registre d’instructions (IR) sur n bits (n=2) qui garde les instructions courantes.

- Un registre Bypass sur 1 bit (Bypass).

- Un registre d’identification optionnel sur 32 bits capable d’être chargé avec un code d’identification du composant.

Un seul registre peut être connecté du TDI vers le TDO (par exemple le registre IR, Bypass, Ident…). La sélection du registre se fait par le décodage du registre d’instruction (IR).

Nous allons voir dans le détail chacune des parties qui composent cette architecture.

7. Le Test Access Port

La représentation du Test Access Port (TAP) est donnée dans la figure ci-dessous :

Figure 5.7 : Test Access Port (TAP)

Le TAP est donc constitué de quatre signaux et d’un signal optionnel :

· Test Data In (TDI) : Signal de test série d’entrée dont la valeur par défaut vaut ‘1’.

· Test Data Out (TDO) : Signal de test série de sortie dont la valeur par défaut vaut ‘Z’. Il n’est actif que pendant l’opération de décalage.

· Test Mode Select (TMS) : Signal de contrôle série d’entrée dont la valeur par défaut vaut ‘1’.

· Test Clock (TCK) : signal fournissant l'horloge au test.

· Test Reset (TRST*) : signal qui contrôle la remise à ‘0’ du TAP dont la valeur par défaut vaut ‘1’. Il est actif sur un niveau bas. C’est ce signal qui est optionnel.

TMS, TCK et TRST* (s’il existe) entrent dans une machine d’état qui produit les changements d’état du signal de contrôle. Ces signaux permettent également de contrôler le registre d’instruction ainsi que les différents registres de données.

La figure 5.8 montre le diagramme de transition du TAP et suffit à la compréhension de son fonctionnement, sachant que la valeur qui va permettre au TAP de changer d’état est celle du TMS et que ce changement d’état est synchrone sur un front montant de l’horloge.

Figure 5.8 : diagramme de transition du TAP

8. Le registre Boundary-Scan

Si nous regardons les cellules JTAG plus attentivement, nous nous rendons compte qu’elles sont chaînées de manière à former le registre Boundary-Scan. L’ordre de la chaîne est déterminé par l’agencement physique des composants sur la carte et/ou par le nombre de couches de la carte. Le registre Boundary-Scan est sélectionné par une instruction commandée au registre d’instructions : instructions Extest, Sample/Preload ou Intest que nous verrons dans le chapitre suivant.

Figure 5.9 : cellule JTAG d’entrée classique

Cette cellule ne permet de réaliser que l’opération de capture et l’opération de décalage. Elle peut être utilisée par exemple pour l’horloge.

La cellule JTAG classique d’entrée/sortie ci-dessous montre une conception d’une cellule JTAG le plus souvent utilisé et qui permet trois modes opératoires : capture, décalage et update.

Figure 5.9 : cellule JTAG d’entrée/sortie classique

Ce type de conception permet d’avoir des bascules D distinctes pour les fonctions de décalage et de maintien. Les données peuvent être transférées à travers le registre Boundary-Scan sans interférer sur la valeur de la section de maintien (qui peut être routée vers le port de données de sortie par l’intermédiaire du multiplexeur de sortie).

La figure 5.9 montre pourquoi une section de maintien est nécessaire :

Figure 5.9 : cellule JTAG avec section de maintien

Cette figure représente un composant JTAG dont les trois sorties vont permettre de contrôler trois RAM par l’intermédiaire de leur Chip-Select (CS).

Dans un mode de fonctionnement normal, seulement une RAM est sélectionnée pour venir dialoguer avec le bus de données. Cela signifie que la plupart des combinaisons de ces trois CS sont interdites.

Il serait impossible de garder une séquence interdite si les données étaient transférées sur le chemin JTAG sans l’élément de maintien et sans le multiplexeur de sortie.

Si le multiplexeur autorisait le passage de la valeur générée par le noyau logique, nous pourrions avoir un problème.

Une solution simple est d’inclure la section de maintien et d’utiliser l’instruction Sample/Preload (que nous verrons dans le chapitre suivant) pour charger une valeur de sécurité dans la section de maintien.

9. Le registre d’instructions

Un registre d’instructions est composé d’un registre à décalage, qui peut être connecté au TDI et au TDO, et une section de maintien qui garde les instructions courantes comme le montre la figure 5.10.

Figure 5.10 : registre d’instructions

Il peut y avoir plusieurs décodeurs logiques entre ces deux sections (cela va dépendre de la taille du registre ainsi que du nombre d’instructions). Le signal de contrôle du registre d’instructions est issu du contrôleur du TAP et permet soit de décaler les valeurs d’entrée/sortie vers le registre à décalage du registre d’instruction soit de charger directement vers la section de maintien (opération ‘update’ le contenu du registre à décalage. Il est donc possible de charger (opération ‘capture’) certaines valeurs vers le registre à décalage du registre d’instruction.

La taille du registre d’instructions doit être d’au moins 2 bits (pour permettre les différentes instructions : Bypass, Sample/Preload, Extest) mais sa taille maximale n’est pas définie.

9.1. Les différentes instructions

L’architecture IEEE 1149.1 impose trois instructions qui sont :

Bypass : L’instruction Bypass permet de passer au travers des composants avec un bit de décalage. Tous les bits doivent être à ‘1’ pour qu’elle soit exécutée.

Extest : L’instruction Extest sélectionne le registre Boundary-Scan en déconnectant le composant JTAG. Elle prépare au test des interconnections. Tous les bits doivent être à ‘0’ pour qu’elle soit exécutée. Sa taille de code n’est pas définie.

Sample/Preload : L’instruction Sample/Preload sélectionne le registre Boundary-Scan mais sans déconnecter le composant JTAG.

Le standard IEEE 1149.1 autorise un certain nombre d’instructions optionnelles qui sont les suivantes :

Intest : Elle sélectionne le registre Boundary-Scan pour le préparer au test du noyau logique interne.

Idcode : Elle sélectionne le registre d’identification placé entre TDI et TDO pour le préparer au chargement du code Idcode et à sa lecture au travers le TDO. Si l’instruction Idcode est chargée, il n’y a pas de registre d’identification présent sur la carte et l’instruction Idcode peut être vu comme si l’utilisateur chargeait l’instruction Bypass.

Runbist : C’est l’instruction qui initialise une routine de test interne et charge le résultat dans le registre placé entre le TDI et le TDO.

En 1993 une révision du standard IEEE 1149.1 apporte deux nouvelles instructions :

Clamp : C’est une instruction qui pilote la valeur de présélection vers la sortie de certains composants et qui sélectionne le registre Bypass entre TDI et TDO.

High : C’est une instruction similaire à Clamp mis à part le fait qu’elle permet de laisser la valeur des broches des composants de sortie sur un niveau logique haute impédance. Elle va également sélectionner le registre Bypass entre TDI et TDO.

Remarque : A l’exception de Bypass, le code de toutes les autres instructions n’est pas défini. La taille minimale du registre d’instructions est de 2 bits et sa taille maximale est indéfinie.

10. Le registre Bypass

Le registre Bypass est un registre sur 1 bit, sélectionné par l’instruction Bypass et qui provient de la fonction de décalage. Il n’y a pas de sortie parallèle (ce qui signifie que le signal de contrôle Update_DR n’agit pas sur le registre). Au contraire, le signal de contrôle Capture_DR agit sur le registre et l’autorise à garder une valeur de ‘0’.

Figure 5.11 : schéma classique d’un registre Bypass

11- Le registre d’identification

Le registre optionnel d’identification est un registre 32 bits qui contient les opérations de capture et de décalage. Une fois que l’opération de capture a été réalisée, le code d’identification sur 32 bits peut être chargé vers TDO pour une inspection. La figure ci-dessous montre une manière possible d’incrémenter une cellule du registre 32 bits.

Figure 5.12 : registre d’identification

12. Les différents types de test

12.1. Test de l’infrastructure

Le test de l’infrastructure permet de vérifier que le Test Access Port (TAP) est correctement relié aux composants JTAG. Cela signifie qu’il va vérifier que la chaîne de scan est établie correctement. Il s’agit donc de la première étape à réaliser.

12.2. Test des interconnections

Le test des interconnections vérifie que les connections entre les différents composants JTAG sont correctement réalisées. Il va donc pouvoir détecter des circuits ouverts, des courts-circuits, de mauvaises soudures, des circuits mal alignés …

12.3. Test du Buswire

Le test du buswire est utilisé lorsque des drivers de bus sont présents sur la carte.

Il test donc les driver un par un, ainsi que toutes leurs opérations (receivers, drivers, bi-directionnel). Différents bus sont testés en parallèle.12.4. Test des clusters

Le test des clusters permet de tester les composants non JTAG entourés des composants JTAG d’une carte électronique. En fait, dans ce contexte, les cellules JTAG agissent comme des récepteurs pour tester les composants ‘non JTAG’ (en général, il s’agit de portes logiques).

12.5. Test de la mémoire

Ce test permet de tester toutes les broches de la mémoire ainsi que ses connexions. L'utilisateur fournit une description de la mémoire à tester (bus d'adresse, bus de donnée, bus de contrôle) et le compilateur génère une série de vecteurs de test (Memory Pattern Generator) à appliquer sur la carte.

Après avoir vu quels types de test il est possible de réaliser avec la gamme ScanPlus, nous étudions maintenant chacun de ces logiciels en expliquant leur rôle d’une part et leur fonctionnement d’autre part. Cependant étant donné que chacun de ces logiciels nécessitent un certain nombre de fichiers pour leur fonctionnement (soit directement, soit indirectement), nous allons auparavant nous intéresser à l’étude de ces fichiers.

13. Exemple de logiciels de Test ScanPlus

Les logiciels de test ScanPlus sont des applications 32-bit comportants plusieurs éléments:

Les logiciels proposés sont les suivants :· ScanPlus TPG

· ScanPlus Runner (programmation de mémoire Flash et CPLD intégré)

· ScanPlus Debugger

· ScanPlus Flash

La figure 5.3 montre les fonctionnalités de ces différents logiciels ainsi que leurs interactions.

Figure 5.13 : Digramme

13.1. Les différents fichiers

Différents types de fichiers sont nécessaires pour la génération des vecteurs de test (ScanPlus TPG).Vous pourrez trouver leur description ainsi qu’un exemple.

Les fichiers Netlist (*.net) :

Ce fichier doit contenir la description de toutes les broches et des nœuds de la carte électronique. Les logiciels de la gamme ScanPlus acceptent la pluspart des fichiers du type CAE/CAD.

Les fichiers BSDL (*.bsd) :

Les fichiers BSDL sont des fichiers donnés par le constructeur du composant JTAG et contiennent toutes les informations relatives à celui-ci. Ils sont écrits en Boundary-Scan Description Language (BSDL) qui est un dérivé du VHSIC Hardware Description Language (VHDL).

Exemple d’un fichiers BSDL d’une bascule D (la 74bct8374) :

entity ttl74bct8374 is generic (PHYSICAL_PIN_MAP : string := "DW_PACKAGE"); port (CLK:in bit; Q:out bit_vector(1 to 8); D:in bit_vector(1 to 8); GND, VCC:linkage bit; OC_NEG:in bit; TDO:out bit; TMS, TDI, TCK:in bit); use STD_1149_1_1990.all; -- Get Std 1149.1-1990 attributes and definitions attribute PIN_MAP of ttl74bct8374 : entity is PHYSICAL_PIN_MAP; constant DW_PACKAGE:PIN_MAP_STRING:="CLK:1, Q:(2,3,4,5,7,8,9,10), " & "D:(23,22,21,20,19,17,16,15)," & "GND:6, VCC:18, OC_NEG:24, TDO:11, TMS:12, TCK:13,TDI:14"; constant FK_PACKAGE:PIN_MAP_STRING:="CLK:9, Q:(10,11,12,13,16,17,18,19)," &"D:(6,5,4,3,2,27,26,25)," & "GND:14, VCC:28, OC_NEG:7, TDO:20, TMS:21, TCK:23, TDI:24"; attribute TAP_SCAN_IN of TDI : signal is true; attribute TAP_SCAN_MODE of TMS : signal is true; attribute TAP_SCAN_OUT of TDO : signal is true; attribute TAP_SCAN_CLOCK of TCK : signal is (20.0e6, BOTH); attribute INSTRUCTION_LENGTH of ttl74bct8374 : entity is 8; attribute INSTRUCTION_OPCODE of ttl74bct8374 : entity is "BYPASS (11111111, 10001000, 00000101, 10000100, 00000001)," & "EXTEST (00000000, 10000000)," & "SAMPLE (00000010, 10000010)," & "INTEST (00000011, 10000011)," & "TRIBYP (00000110, 10000110)," & -- Boundary Hi-Z "SETBYP (00000111, 10000111)," & -- Boundary 1/0 "RUNT (00001001, 10001001)," & -- Boundary run test "READBN (00001010, 10001010)," & -- Boundary read normal "READBT (00001011, 10001011)," & -- Boundary read test "CELLTST(00001100, 10001100)," & -- Boundary selftest normal "TOPHIP (00001101, 10001101)," & -- Boundary toggle out test "SCANCN (00001110, 10001110)," & -- BCR Scan normal "SCANCT (00001111, 10001111)"; -- BCR Scan test attribute INSTRUCTION_CAPTURE of ttl74bct8374 : entity is "10000001"; attribute INSTRUCTION_DISABLE of ttl74bct8374 : entity is "TRIBYP"; attribute REGISTER_ACCESS of ttl74bct8374 : entity is "BOUNDARY (READBN, READBT, CELLTST)," & " BYPASS (TOPHIP, SETBYP, RUNT, TRIBYP)," & "BCR[2] (SCANCN, SCANCT)"; -- 2-bit Boundary Control Register attribute BOUNDARY_CELLS of ttl74bct8374 : entity is "BC_1"; attribute BOUNDARY_LENGTH of ttl74bct8374 : entity is 18; attribute BOUNDARY_REGISTER of ttl74bct8374 : entity is -- num cell port function safe [ccell disval rslt] "17 (BC_1, CLK, input, X)," & "16 (BC_1, OC_NEG, input, X)," & -- Merged Input/Control "16 (BC_1, *, control, 1)," & -- Merged Input/Control "15 (BC_1, D(1), input, X)," & "14 (BC_1, D(2), input, X)," & "13 (BC_1, D(3), input, X)," & "12 (BC_1, D(4), input, X)," & "11 (BC_1, D(5), input, X)," & "10 (BC_1, D(6), input, X)," & "9 (BC_1, D(7), input, X)," & "8 (BC_1, D(8), input, X)," & "7 (BC_1, Q(1), output3, X, 16, 1, Z)," & -- cell 16 @ 1 -> Hi-Z. "6 (BC_1, Q(2), output3, X, 16, 1, Z)," & "5 (BC_1, Q(3), output3, X, 16, 1, Z)," & "4 (BC_1, Q(4), output3, X, 16, 1, Z)," & "3 (BC_1, Q(5), output3, X, 16, 1, Z)," & "2 (BC_1, Q(6), output3, X, 16, 1, Z)," & "1 (BC_1, Q(7), output3, X, 16, 1, Z)," & "0 (BC_1, Q(8), output3, X, 16, 1, Z)"; end ttl74bct8374;13.2. ScanPlus Test Generator (TPG)

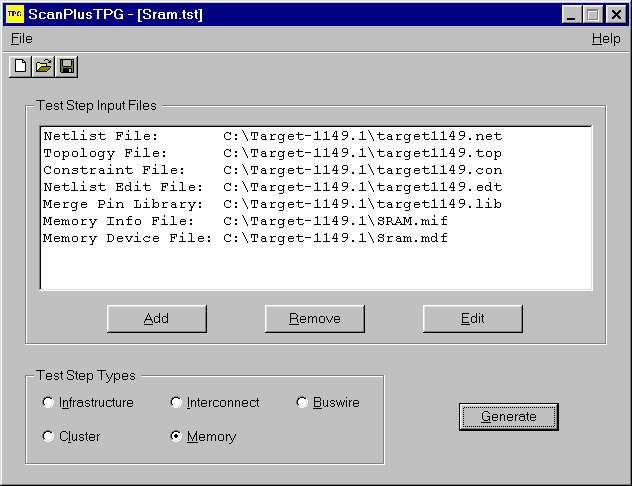

Comme son nom l’indique ce logiciel permet de générer les vecteurs de test de la carte. Le compilateur contenu dans ce logiciel est un compilateur Hewlett-Packard (HP3070). C’est donc un produit de qualité dont la vitesse d’action étonne les utilisateurs car la durée des tests est de l’ordre de quelques secondes (Cette vitesse d’action n’est donnée qu’à titre indicatif puisqu’elle va évidemment varier en fonction de la carte à tester).

ScanPlus TPG convertit tous les fichiers dont il a besoin (son besoin en fichier dépends du type de test que l’on souhaite réaliser) pour n’en former qu’un seul du type compact vector format (CVF). Ce fichier du type compact vector format est donc le fichier qui contient les vecteurs de test correspondant au type de test que l’on souhaite réaliser. ScanPlus TPG va donc générer 5 vecteurs de test au maximum correspondant à chacun des 5 tests décris dans la partie précédente. Afin de générer ces vecteurs de test, ScanPlus TPG passe par la création de fichiers intermédiaires.

Ce logiciel fait partie des logiciels optionnels puisqu’Elexience propose à ses clients de réaliser elle-même cette étape. En réalité cela n’est rentable pour le client que s’il n’envisage de réaliser que très peu d’applications (au-delà de 2 ou 3 applications, il devient plus avantageux de faire l’acquisition de ce logiciel).

Une fois les vecteurs de tests générés, il devient possible de tester la carte électronique en appliquant ces vecteurs de test à la carte électronique. C’est le rôle que va jouer ScanPlus Runner.

12.3. ScanPlus Runner

La liaison entre la carte électronique à tester et le poste de travail se fait par l’intermédiaire du bus JTAG.

ScanPlus Runner est en fait un des logiciels phare de la gamme de Corelis puisque c’est le logiciel qui permet d’appliquer sur la carte à tester les vecteurs de test générés par ScanPlus TPG. Il permet trois modes de diagnostic :

Le mode GO/NO-GO :

Avec ce type de diagnostic, ScanPlus Runner vérifie le fonctionnement de la carte sans rentrer dans les détails. Il renvoie simplement à l’utilisateur si le test qu’il a effectué est passé ou non.

Le diagnostic de base :

Lorsque l’utilisateur sélectionne ce type de fonctionnement l’idée est la même que précédemment mais s’il y a dysfonctionnement, il permet de visualiser la table de vérité donc d’en déduire d’où provient ce dysfonctionnement.

Le diagnostic avancé :

Pour ce mode de fonctionnement, ScanPlus Runner va effectuer exactement les mêmes tests que précédemment mais en cas de dysfonctionnement, il va indiquer précisément d’où provient ce dysfonctionnement et les manipulations possibles à effectuer par l’utilisateur pour le faire disparaître.

De plus ScanPlus Runner intègre la fonction In-System-Programming (ISP) permettant le téléchargement de programme à l'intérieur de circuits programmables (FPAG's, CPLD's, ASIC's) de toutes marques au format SVF ou JAM. Il permet également de programmer les mémoires FLASH à l'aide du fichier généré par ScanPlus Flash Generator.

ScanPlus Runner propose également en standard des drivers de haut niveau (Labwindows CVI, Labview et programmation en ligne) afin de créer sa propre interface de test.

13.4. ScanPlus Debugger

ScanPlus Debugger permet de venir regarder la valeur de la sortie d’une ou d’un groupement de broches (dans ce cas il y a donc création d’un bus) en fonction de la valeur que l’utilisateur a décidé de lui appliquer en entrée. Cette valeur peut être obtenue aussi bien en binaire, qu’en décimal mais également en hexadécimal. D’où son nom de ScanPlus Debugger puisqu’on peut debugger virtuellement la carte et appliquer ces modifications lors de la mise au point de nouveaux prototypes. Un test d'infrastructure est également disponible.

13.5. ScanPlus Flash

ScanPlus Flash fait partie des logiciels qui utilisent d’autres fonctions du bus JTAG que le test. En effet ce logiciel utilise le bus JTAG pour le téléchargement de données (code) à l’intérieure de mémoires Flash.