Technologie de la famille TTL

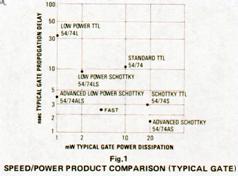

Toutes les familles TTL présentent d'excellentes caractéristiques, Il est cependant important de faire des distinctions entre elles sur certains points essentiels : à savoir la dissipation de puissance, la vitesse et la plus ou moins grande sensibilité aux charges capacitives. La figure 1 illustre la relation entre la dissipation de puissance et la vitesse (temps de propagation). Pour différencier les familles, on utilise les indications suivantes :

L : Low Power = dissipation de puissance extrêmement faible

LS : Low Power Schottky = dissipation de puissance extrêmement faible et temps de propagation court

ALS : Advanced Low Power Schottky = dissipation de puissance extrêmement faible et temps de propagation extrêmement court

S : Schottky = dissipation de puissance normale et temps de propagation court

AS : Advanced Schottky = dissipation de puissance normale et temps de propagation extrêmement court

Aucune indication = caractéristiques normales.

Dans deux types de circuits intégrés de la famille, à savoir les types TTL et L-TTL, les transistors intégrés deviennent conducteurs aussitôt que le courant de base est suffisant pour le gain en courant minimal. Normalement, le fonctionnement est différent. En effet, le courant de base d'un transistor moyen (à gain en courant plus élevé) est plus élevé que ce qui est nécessaire, ce qui contribue à accélérer l'entrée en saturation du transistor. Lorsqu'il s'agit de commuter un tel transistor pour qu'il se bloque à nouveau, cet excès de charge de la base provoque un rallongement considérable du temps de commutation. Un dopage à base d'or est généralement utilisé pour accélérer l'effondrement de cette charge, ce qui se paye par une diminution notable du gain en courant.

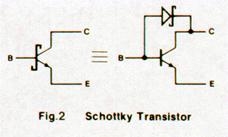

La mise en uvre d'une diode Schottky de pincement supplémentaire (figure 2) permet d'obtenir d'excellents résultats. Celle-ci est caractérisée notamment par une faible chute de tension directe (0,3 V), et se trouve montée entre la base et le collecteur. Lorsque le transistor arrive en saturation le courant d'entrée excédentaire ne transite plus par la base, mais se voit acheminé vers le collecteur via la diode de pincement. De sorte que le transistor n'est jamais tout à fait saturé d'une part et se bloque d'autre part aussitôt que le courant de base disparaît. Comme le dopage à base d'or n'est plus nécessaire, le gain en courant du transistor n'est pas affecté ; le courant de base peut être plus faible et la commutation du transistor se fait plus rapidement.Les types ALS et AS font appel à une technologie différente qui réduit considérablement les capacités parasites et le temps de propagation. Le rapport vitesse/dissipation est nettement meilleur que dans les technologies d'intégration antérieures. Par rapport à un circuit LS, le circuit ALS correspondant offre une vitesse sensiblement plus élevée pour une dissipation sensiblement plus faible. Tandis qu'un circuit du type AS offre, par rapport à son homonyme du type S, un temps de propagation deux fois plus court pour une dissipation identique.

La famille LS

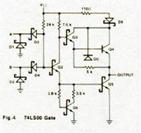

A quelques exceptions près, les circuits de la famille LS ne sont pas dotés d'entrées à émetteurs multiples, laquelle structure avait donné son nom à la famille TTL. La plupart des circuits LS ont un circuit d'entrée du type DTL, avec des diodes Schottky de pincement pour assurer la fonction AND, comme le montrent les diodes D3 et D4 sur la figure 4. Comparé au circuit classique à émetteurs multiples, ce circuit nouveau est plus rapide et sa tension de claquage est beaucoup plus élevée. La tension d'entrée maximale lors des tests a pu être portée à 10 V sans que l'on ait pu constater de détérioration des caractéristiques. La tension de claquage garantie se révèle être de 15 V ou plus.Dans la famille TTL, la fonction des diodes est uniquement de supprimer les courants transitoires; elles ne sauraient jouer un rôle de protection statique contre les tensions d'entrées négatives. Si le courant à travers ces diodes excède 2 mA pendant plus de 500 ns, il se peut qu'il apparaisse un transistor NPN parasite, qui à son tour draine du courant sur le circuit LS et provoque des erreurs logiques.

La capacité effective d'une entrée TTL en boîtier DIP est de 5 pF. Lorsque cette entrée assure plus d'une fonction interne, il faut compter 1,5 pF supplémentaires par fonction.

Entrées inutilisées

Théoriquement, une entrée inutilisée est supposée être au niveau logique haut, mais en pratique il s'agit d'un "peut-être" logique qui peut se comporter comme une antenne pour le bruit. Il suffit de quelques centaines de millivolts de bruit pour que cette entrée en l'air passe au niveau logique bas. Il convient donc, dans les circuits comportant des mémoires, des bascules, des registres ou des compteurs, de définir, par une polarisation appropriée, le niveau logique des entrées non utilisées. Les circuits qui ne tiennent pas compte de cette remarque importante ne sont à utiliser qu'avec circonspection.

Si la fonction logique nécessite des entrées au niveau logique bas, telles les portes NOR ou OR, les entrées inutilisées seront mises au niveau logiques bas (reliées à la masse). Lorsque le niveau logique d'entrée doit être haut, il suffit de relier ces entrées inutilisées à VCC. Une résistance de limitation de courant d'environ 1...5 k est recommandée pour les entrées à émetteur qui claquent avec des tensions supérieures à 5,5 V, Des imperfections de l'alimentation ou toute autre erreur de manipulation peuvent causer des dommages irréparables si le courant n'est pas limité. Remarquer qu'une résistance de limitation peut desservir plusieurs entrées, à condition que la somme des courants d'entrée ne fasse pas s'effondrer la tension en-dessous du seuil de 2,4 V. On se souviendra également du fait que les circuits d'entrée de la famille TTL-LS à diode Schottky se caractérisent par une tension de claquage supérieure à 15 V et que, pas conséquent, elles ne requièrent pas absolument cette mesure de limitation de courant. Il est donc permis de relier une entrée inutilisée à une autre entrée, utilisée et ayant la même fonction, comme par exemple dans les portes NAND et AND, à condition que la source de courant puisse fournir le courant IIH supplémentaire. Cette pratique est déconseillée pour les familles TTL-LS dans un environnement bruyant, parce que chaque diode présente une capacité faible et que deux ou plusieurs d'entre elles connectées en parallèle sont susceptibles d'introduire des parasites d'origine capacitive qui viendront se superposer au niveau logique supposé haut. Ceci peut entraîner un blocage momentané du transistor Q2 (figure 4).

Caractéristiques de sortie

La figure 9 donne les caractéristiques d'une sortie TTL standard au niveau logique bas, à trois températures différentes. La tension de sortie présente un décalage de quelques 90 mV hors charge. Avec une température de 25°C, la pente correspond à une résistance de saturation de 8 ohms, à 125°C de 9 ohms, et à 55°C de seulement 6 ohms. A faible température, le gain du transistor est si faible qu'un courant de 25 mA suffit déjà à saturer le transistor de sortie.

La figure 10 donne les caractéristiques de sortie d'une porte de la famille LS-TTL au niveau logique bas. Lorsque la valeur du courant de sortie IOL est faible, le transistor de polarisation au niveau logique bas se sature rapidement, réduisant ainsi le temps de propagation. Les courbes indiquent également ce qui se produit lorsque le courant de sortie devient négatif. Dans les circuits LS-TTL, le dispositif de verrouillage anti-saturation (clamping) du transistor Q5 entraîne une tension de sortie au niveau logique bas pour un courant donné plus élevée que dans d'autres types de circuits .

Lorsque la sortie est au niveau logique haut, elle procure une faible impédance et se révèle capable de fournir des courants importants. La figure 11 donne les caractéristiques de sortie d'une porte TTL standard au niveau logique haut à trois températures différentes. Hors charge et à 25°C, la tension VOH est d'environ 3,5 V. Lorsque le courant IOH croît jusqu'à 6 mA environ, la caractéristique correspond à une tension fixe moins la chute de tension, à croissance logarithmique, à travers deux jonctions PN. Lorsque IOH dépasse 6 mA, le transistor de polarisation au niveau logique haut Q3 (figure 3) entre en saturation et la pente de la caractéristique correspond à la résistance de limitation de 130 ohms plus la résistance de saturation de Q3. La valeur maximale d'IOH, là où la caractéristique coupe l'axe horizontal, est en corrélation avec le paramètre IOS (le courant de court-circuit) ; on la considère souvent comme une mesure de l'aptitude du circuit à supporter des charges capacitives.

Interfaçage de circuits TTL et CMOS

Avec une tension d'alimentation de 5 V, une sortie CMOS de la série B (avec tampon = buffered) est capable de drainer 0,5 mA à VOL=0,4 V, ce qui correspond aux caractéristiques d'entrée d'un circuit TTL-LS. Si la tension d'alimentation du circuit CMOS est supérieure à 5 V, le circuit LS-TTL doit être un de ceux qui sont dotés d'une entrée à diode (et non à émetteur). De sorte que la tension VOH élevée du circuit CMOS (= sa tension d'alimentation) ne provoquera pas le claquage de l'entrée du circuit TTL. Le seuil VIH d'une entrée CMOS peut-être de l'ordre de 70% de la tension d'alimentation, tandis que le seuil inférieur VIL ne devra pas être inférieur à 30% de cette même tension d'alimentation. Par conséquent, un signal de sortie TTL est satisfaisant au niveau logique bas, mais une résistance de polarisation au niveau logique haut est nécessaire sur l'entrée CMOS pour garantir un niveau logique haut convenable. Cette résistance devra être reliée à la tension d'alimentation à condition que celle-ci ne dépasse pas 5,5 V. Si cela devait être le cas, il faut veiller à ce que le circuit TTL soit en mesure de s'accommoder de cette tension excessive. Dans le cas contraire, il faut renoncer à cette forme d'interfaçage.

Entrance et sortance (fan in, fan out) :

Augmentation de la sortance

On peut, afin d'augmenter la sortance, mettre en parallèle plusieurs entrées ou sorties de portes. Toutefois, il faut limiter le nombre de portes mises en parallèle à celui des portes intégrées dans un même boîtier. Ceci notamment afin d'éviter des perturbations sur les lignes d'alimentation dues aux différences entre les temps de propagation de chaque boîtier. Il n'y a, en fait, aucun inconvénient pour les circuits eux-mêmes, mais il pourrait en résulter des perturbations de la logique et de la chronologie.

Caractéristiques d'entrée

La figure 7 donne les caractéristiques d'entrée (courant/ tension) d'un tampon TTL. Lorsque la tension d'entrée atteint quelques 6 V, il se produit le phénomène dit d'avalanche, qui se caractérise par une très faible résistance-série, et une augmentation rapide du courant d'avalanche parallèlement à l'augmentation de la tension d'entrée. Pour éviter une détérioration irrémédiable, il faut soit que le courant d'entrée soit limité à 5 mA ou moins, soit que la tension d'entrée ne puisse excéder 5,5 V. Tant que la tension d'entrée se situe entre 2 V et 5,5 V, le courant d'entrée IIH d'une seule entrée ne doit jamais dépasser 40 µA ou 50 µA - selon la famille TTL. Lorsque la tension d'entrée chute sous le seuil de 2 V, un courant issu de l'entrée commence à circuler, et croît très rapidement à mesure que la tension décroît. Dans cette plage, la pente de la caractéristique n'est plus que de quelques 200 ohms, révélant ainsi qu'une partie du courant à travers la résistance de polarisation au niveau logique haut continue de circuler à travers les jonctions internes du circuit. C'est là que commence la plage de transition : à un moment donné, le transistor de polarisation au niveau logique bas ne reçoit plus le courant de base suffisant pour entretenir la saturation, et la sortie passe du niveau logique bas au niveau logique haut.

Lorsque la tension d'entrée passe d'environ 1 V à 0,5 V, la pente de la caractéristique est égale à la valeur de la résistance de polarisation au niveau logique haut. Dans ce cas, ce sont environ 2 k. Lorsque la tension d'entrée tombe sous le seuil de 0,7 V, le courant augmente rapidement dès que la diode d'entrée devient conductrice.

La figure 8 montre les caractéristiques d'une entrée de la famille LS-TTL. La tension de claquage est typiquement supérieurement à 15 V, et le courant de fuite de l'entrée est négligeable à partir de 1,5 V. Lorsque la tension d'entrée passe en-dessous de 1,3 V, le courant de la porte commence à s'écouler vers l'extérieur et c'est là que commence la plage de commutation. Pour une tension d'entrée de 1 V à 0,3 V, la pente de la caractéristique d'entrée est celle de la résistance de polarisation au niveau logique haut de 24 k. La diode Schottky devient passante et le courant augmente rapidement à partir du moment où la tension d'entrée devient inférieure à 0,3 V.

Tension d'alimentation et température

La tension d'alimentation nominale de tous les circuits TTL est de +5 V. La tolérance est de 5% (250 mV) sur toute la plage de température de 0° à 75°C (pour certains seulement jusqu'à 70°C). La température réelle de la jonction peut être calculée en multipliant la dissipation de puissance du circuit intégré par la résistance thermique du boîtier, puis en ajoutant la température ambiante TA ou la température du boîtier TC.

DEFINITIONS

Introduction

Les termes et symboles mentionnés ci-après sont conformes aux normes internationales de l'International Electrotechnical Commission (IEC).

Conditions de fonctionnement et définitions

Courant

Courant d'entrée au niveau logique haut

(high level input current) IIH

Le courant circulant dans une entrée lorsqu'elle est mise au niveau logique haut.

Courant de sortie au niveau logique haut

(high level output current) IOH

Le courant circulant dans une sortie au niveau logique haut.

Courant d'entrée au niveau logique bas

(low level input current) IIL

Le courant circulant dans une entrée au niveau logique bas.

Courant de sortie au niveau logique bas

(low level output current) IOL

Le courant circulant dans une sortie au niveau logique bas.

Courant d'alimentation

(supply current) ICC

Le courant circulant par la broche d'alimentation d'un circuit intégré

Note : pour un courant fourni par la broche d'un circuit intégré, la valeur indiquée est précédée du signe "".

Temps de maintien (hold time) th

L'intervalle de temps pendant lequel un signal doit être retenu sur une broche d'entrée donnée après qu'un flanc actif se soit produit sur une broche d'entrée donnée.

Le temps de maintien est le temps réel entre deux événements et peut se révéler trop court pour l'obtention du résultat escompté. On spécifie une valeur minimale qui est lintervalle le plus court pour lequel le fonctionnement du circuit est garanti.

La valeur du temps de maintien peut être négative : dans ce cas, elle définit l'intervalle le plus long pour lequel le fonctionnement est garanti.

Temps de propagation (propagation time)

Durée du retard pour une transition d'un niveau logique bas vers un niveau logique haut en sortie tPLH

Le temps entre les points de référence indiqués sur les courbes de tension d'entrée et de sortie lorsqu'une sortie passe d'un niveau logique bas défini à un niveau logique haut défini.

Durée du retard pour une transition d'un niveau logique haut vers un niveau logique bas en sortie tPHL

Le temps entre les points de référence indiqués sur les courbes de tension d'entrée et de sortie lorsqu'une sortie passe d'un niveau logique haut défini à un niveau logique bas défini.

Temps d'établissement (set up time) tsu

Le temps entre l'application d'un signal d'entrée stable sur une broche donnée et l'apparition du flanc actif d'entrée correspondant sur une autre broche.

Le temps d'établissement est le temps réel entre deux événements et peut se révéler insuffisant pour l'achèvement de l'établissement. Il s'agit d'une valeur minimale à respecter si l'on veut rester dans les limites spécifiées pour le fonctionnement garanti du circuit.

La valeur peut être négative ; dans ce cas elle définit l'intervalle le plus long admis pour le fonctionnement normal du circuit.

Tension (voltage)

Tension d'entrée au niveau logique haut

(high level input voltage) VIH

Une tension d'entrée comprise dans la plus positive des deux plages de tension définies pour représenter les deux niveaux logiques. On spécifie une valeur minimale qui est la moins positive des valeurs possibles correspondant à un niveau logique haut et avec laquelle le fonctionnement du circuit est garanti.

Tension de sortie au niveau logique haut

(high level output voltage) VOH

La tension sur une broche de sortie lorsque les conditions d'entrée du circuit sont celles qui, selon les spécifications du produit, doivent produire un niveau logique haut en sortie.

Tension d'entrée au niveau logique bas

(low level input voltage) VIL

Une tension d'entrée comprise dans la plus négative ou moins positive des deux plages de tension définies pour représenter les deux niveaux logiques. On spécifie une valeur maximale qui est la plus positive des valeurs admises pour représenter un niveau logique bas et pour laquelle le fonctionnement du circuit est garanti.

Tension de sortie au niveau logique bas

(low level output voltage) VOL

La tension sur une broche de sortie lorsque les conditions d'entrée du circuit sont celles qui, selon les spécifications du produit, doivent produire un niveau logique bas en sortie.